# **KPS Series, High Voltage, X7R Dielectric,** 500 – 630 VDC (Commercial Grade)

#### **Overview**

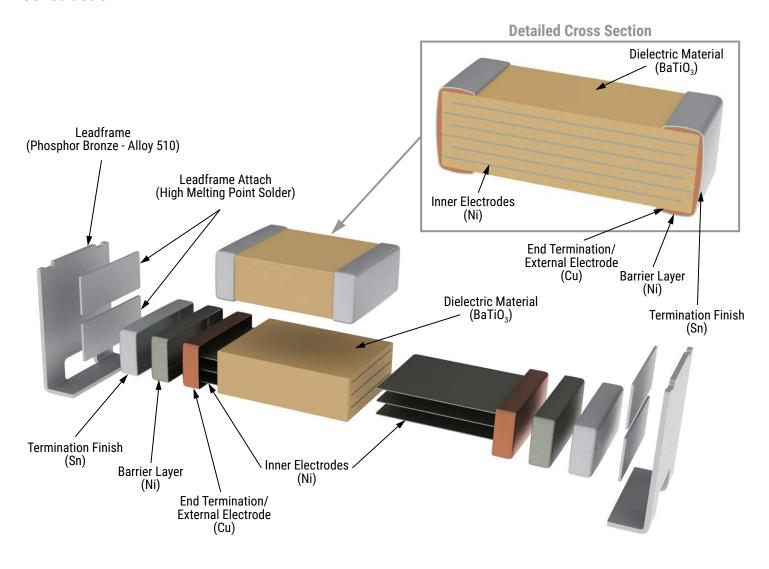

KEMET Power Solutions (KPS) High Voltage stacked capacitors utilize a proprietary lead-frame technology to vertically stack one or two multilayer ceramic chip capacitors into a single compact surface mount package. The attached lead-frame mechanically isolates the capacitor(s) from the printed circuit board, thereby offering advanced mechanical and thermal stress performance. Isolation also addresses concerns for audible microphonic noise that may occur when a bias voltage is applied. A two-chip stack offers up to double the capacitance in the same or smaller design footprint when compared to traditional surface mount MLCC devices. Providing up to 10 mm of board flex capability, KPS Series High Voltage capacitors are environmentally friendly and in compliance with RoHS legislation.

KEMET's KPS Series devices in X7R dielectric exhibit a predictable change in capacitance with respect to time and voltage, and boast a minimal change in capacitance with reference to ambient temperature. Capacitance change is limited to ±15% from -55°C to +125°C. These devices are capable of Pb-Free reflow profiles and provide lower ESR, ESL and higher ripple current capability when compared to other dielectric solutions.

Conventional uses include both snubbers and filters in applications such as switching power supplies and lighting ballasts. Their exceptional performance at high frequencies has made high voltage ceramic capacitors the preferred dielectric choice of design engineers worldwide. In addition to their use in power supplies, these capacitors are widely used in industries related to automotive (hybrid), telecommunications, medical, military, aerospace, semiconductors, and test/diagnostic equipment.

#### **Benefits**

- -55°C to +125°C operating temperature range

- · Reliable and robust termination system

- EIA 2220 case size

- DC voltage ratings of 500 V and 630 V

- Capacitance offerings ranging from 0.047 μF up to 1.0 μF

- Available capacitance tolerances of ±10% and ±20%

- Higher capacitance in the same footprint

- · Potential board space savings

# **Ordering Information**

| C       | 2220                  | C                        | 105                                         | M                                     | С                         | R          | 2                                                            | C                             | 7186                                                         |

|---------|-----------------------|--------------------------|---------------------------------------------|---------------------------------------|---------------------------|------------|--------------------------------------------------------------|-------------------------------|--------------------------------------------------------------|

| Ceramic | Case Size<br>(L"x W") | Specification/<br>Series | Capacitance<br>Code (pF)                    | Capacitance<br>Tolerance <sup>1</sup> | Rated<br>Voltage<br>(VDC) | Dielectric | Failure Rate/<br>Design                                      | Leadframe Finish <sup>2</sup> | Packaging/<br>Grade<br>(C-Spec)                              |

|         | 2220                  | C =<br>Standard          | Two significant digits and number of zeros. | K = ±10%<br>M = ±20%                  | C = 500<br>B = 630        | R = X7R    | 1 = KPS Single<br>Chip Stack<br>2 = KPS Double<br>Chip Stack | C = 100% Matte Sn             | See "Packaging<br>C-Spec Ordering<br>Options Table"<br>below |

<sup>&</sup>lt;sup>1</sup> Double chip stacks ("2" in the 13th character position of the ordering code) are only available in M ( $\pm$ 20%) capacitance tolerance. Single chip stacks ("1" in the 13th character position of the ordering code) are available in K ( $\pm$ 10%) or M ( $\pm$ 20%) tolerances.

<sup>&</sup>lt;sup>2</sup> Additional leadframe finish options may be available. Contact KEMET for details.

# **Packaging C-Spec Ordering Options Table**

| Packaging Type <sup>1</sup>               | Packaging/Grade<br>Ordering Code (C-Spec) <sup>2</sup> |

|-------------------------------------------|--------------------------------------------------------|

| 7" Reel (Embossed Plastic Tape)/Unmarked  | 7186                                                   |

| 13" Reel (Embossed Plastic Tape)/Unmarked | 7289                                                   |

<sup>&</sup>lt;sup>1</sup> The terms "Marked" and "Unmarked" pertain to laser marking option of capacitors. All packaging options labeled as "Unmarked" will contain capacitors that have not been laser marked. The option to laser mark is not available on these devices. For more information see "Capacitor Marking".

#### Benefits cont'd

- Advanced protection against thermal and mechanical stress

- · Provides up to 10 mm of board flex capability

- · Reduces audible microphonic noise

- · Extremely low ESR and ESL

- Lead (Pb)-free, RoHS and REACH compliant

- · Capable of Pb-free reflow profiles

- Non-polar device, minimizing installation concerns

- · Film alternative

## **Applications**

Typical applications include switch mode power supplies (input filters, resonators, tank circuits, snubber circuits, output filters), high voltage coupling and DC blocking, lighting ballasts, voltage multiplier circuits, DC/DC converters and coupling capacitors in Ćuk converters. Markets include power supply, LCD fluorescent backlight ballasts, HID lighting, telecom equipment, industrial and medical equipment/control, LAN/WAN interface, analog and digital modems, and automotive (electric and hybrid vehicles, charging stations and lighting applications).

# **Application Note**

X7R dielectric is not recommended for AC line filtering or pulse applications.

## **Qualification/Certification**

Commercial Grade products are subject to internal qualification. Details regarding test methods and conditions are referenced in Table 4, Performance and Reliability.

# **Environmental Compliance**

Lead (Pb)-free, RoHS, and REACH compliant without exemptions.

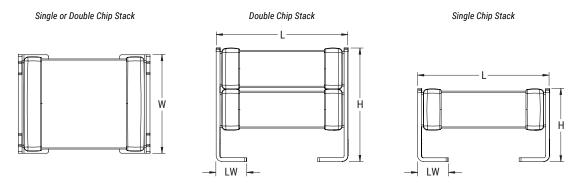

# **Dimensions - Millimeters (Inches)**

| Number of Chips | EIA Size<br>Code | Metric Size<br>Code | L<br>Length                   | W<br>Width                    | H<br>Height                   | LW<br>Lead Width              | Mounting<br>Technique |

|-----------------|------------------|---------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------|

| Single          | 2220             | 5650                | 6.00 (0.236)<br>±0.50 (0.020) | 5.00 (0.197)<br>±0.50 (0.020) | 3.50 (0.138)<br>±0.30 (0.012) | 1.60 (0.063)<br>±0.30 (0.012) | Solder Reflow         |

| Double          | 2220             | 5650                | 6.00 (0.236)<br>±0.50 (0.020) | 5.00 (0.197)<br>±0.50 (0.020) | 5.00 (0.197)<br>±0.50 (0.020) | 1.60 (0.063)<br>±0.30 (0.012) | Only                  |

#### **Electrical Parameters/Characteristics**

| Item                                                               | Parameters/Characteristics                                                                                                                                          |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Temperature Range                                        | -55°C to +125°C                                                                                                                                                     |

| Capacitance Change with Reference to +25°C and 0 Vdc Applied (TCC) | ±15%                                                                                                                                                                |

| <sup>1</sup> Aging Rate (Maximum % Capacitance Loss/Decade Hour)   | 3.0%                                                                                                                                                                |

| <sup>2</sup> Dielectric Withstanding Voltage (DWV)                 | 150% of rated voltage for voltage rating of < 1000V<br>120% of rated voltage for voltage rating of ≥ 1000V<br>(5±1 seconds and charge/discharge not exceeding 50mA) |

| <sup>3</sup> Dissipation Factor (DF) Maximum Limit at 25°C         | 2.5%                                                                                                                                                                |

| <sup>4</sup> Insulation Resistance (IR) Minimum Limit at 25°C      | 1,000 megohm microfarads or 100GΩ<br>(500 VDC applied for 120±5 seconds at 25°C)                                                                                    |

<sup>&</sup>lt;sup>1</sup>Regarding Aging Rate: Capacitance measurements (including tolerance) are indexed to a referee time of 1,000 hours.

$1kHz \pm 50Hz$  and  $1.0 \pm 0.2$  Vrms if capacitance ≤  $10\mu F$

120Hz  $\pm$  10Hz and 0.5  $\pm$  0.1 Vrms if capacitance > 10 $\mu$ F

Note: When measuring capacitance it is important to ensure the set voltage level is held constant. The HP4284 and Agilent E4980 have a feature known as Automatic Level Control (ALC). The ALC feature should be switched to "ON".

#### **Post Environmental Limits**

| High Temperature Life, Biased Humidity, Moisture Resistance |                     |                      |                                   |                      |                          |  |  |  |  |  |

|-------------------------------------------------------------|---------------------|----------------------|-----------------------------------|----------------------|--------------------------|--|--|--|--|--|

| Dielectric                                                  | Rated DC<br>Voltage | Capacitance<br>Value | Dissipation Factor<br>(Maximum %) | Capacitance<br>Shift | Insulation<br>Resistance |  |  |  |  |  |

|                                                             | > 25                |                      | 3.0                               |                      | 10% of Initial<br>Limit  |  |  |  |  |  |

| X7R                                                         | 16/25               | All                  | 5.0                               | ±20%                 |                          |  |  |  |  |  |

|                                                             | < 16                |                      | 7.5                               |                      |                          |  |  |  |  |  |

<sup>&</sup>lt;sup>2</sup>DWV is the voltage a capacitor can withstand (survive) for a short period of time. It exceeds the nominal and continuous working voltage of the capacitor.

<sup>&</sup>lt;sup>3</sup> Capacitance and dissipation factor (DF) measured under the following conditions:

<sup>&</sup>lt;sup>4</sup>To obtain IR limit, divide  $M\Omega$ - $\mu$ F value by the capacitance and compare to  $G\Omega$  limit. Select the lower of the two limits.

Table 1 - Capacitance Range/Selection Waterfall (2220 Case Sizes)

|                   |             | Case Size/Series         |                  | C2220C                                                                                          |     |      |  |  |

|-------------------|-------------|--------------------------|------------------|-------------------------------------------------------------------------------------------------|-----|------|--|--|

|                   |             | Voltag                   | e Code           | С                                                                                               | В   | D    |  |  |

| Capacitance       | Capacitance | Rated Volt               | age (VDC)        | 500                                                                                             | 630 | 1000 |  |  |

|                   | Code        | Capacitance<br>Tolerance |                  | Product Availability and Chip Thickness<br>Codes – See Table 2 for Chip Thickness<br>Dimensions |     |      |  |  |

| Single Chip Stack |             |                          |                  |                                                                                                 |     |      |  |  |

| 0.047 μF          | 473         | К                        | М                | JP                                                                                              | JP  |      |  |  |

| 0.10 μF           | 104         | K                        | M                | JP                                                                                              | JP  |      |  |  |

| 0.15 μF           | 154         | K                        | M                | JP                                                                                              | JP  |      |  |  |

| 0.22 μF           | 224         | K                        | M                | JP                                                                                              | JP  |      |  |  |

| 0.33 μF           | 334         | K                        | M                | JP                                                                                              |     |      |  |  |

| 0.47 μF           | 474         | K                        | M                | JP                                                                                              |     |      |  |  |

|                   |             | Double                   | <b>Chip Stac</b> | k                                                                                               |     |      |  |  |

| 0.10 μF           | 104         |                          | М                | JR                                                                                              | JR  |      |  |  |

| 0.22 μF           | 224         |                          | M                | JR                                                                                              | JR  |      |  |  |

| 0.33 μF           | 334         |                          | M                | JR                                                                                              | JR  |      |  |  |

| 0.47 μF           | 474         |                          | M                | JR                                                                                              | JR  |      |  |  |

| 0.68 μF           | 684         |                          | M                | JR                                                                                              |     |      |  |  |

| 1.0 μF            | 105         |                          | M                | JR                                                                                              |     |      |  |  |

|                   |             | Rated Volt               | age (VDC)        | 500                                                                                             | 630 | 1000 |  |  |

| Capacitance       | Capacitance | Voltag                   | e Code           | С                                                                                               | В   | D    |  |  |

| - apacitailo      | Code        | Case Siz                 | e/Series         | C2220C                                                                                          |     |      |  |  |

These products are protected under US Patent 8,331,078 other patents pending, and any foreign counterparts. SnPb termination options available. "C"(100% Sn) & "L"(SnPb) Terminations.

# Table 2 - Chip Thickness/Tape & Reel Packaging Quantities

| Thickness | Case | Thickness ± | Paper C | <b>Quantity</b> | Plastic Quantity |          |  |

|-----------|------|-------------|---------|-----------------|------------------|----------|--|

| Code      | Size | Range (mm)  | 7" Reel | 13" Reel        | 7" Reel          | 13" Reel |  |

| JP        | 2220 | 3.50 ± 0.30 | 0       | 0               | 300              | 1,300    |  |

| JR        | 2220 | 5.00 ± 0.50 | 0       | 0               | 200              | 800      |  |

Package quantity based on finished chip thickness specifications.

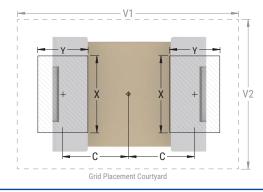

# **Table 3 – KPS Land Pattern Design Recommendations (mm)**

| EIA SIZE<br>CODE | METRIC<br>SIZE | Median (Nominal) Land<br>Protrusion |      |      |      |      |  |  |  |

|------------------|----------------|-------------------------------------|------|------|------|------|--|--|--|

| OODL             | CODE           | C                                   | Y    | X    | V1   | V2   |  |  |  |

| 2220             | 5650           | 2.69                                | 2.08 | 4.78 | 7.70 | 6.00 |  |  |  |

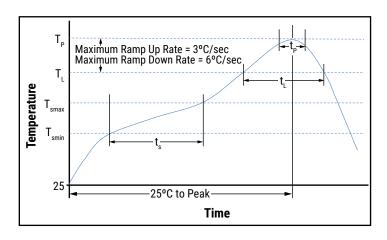

## **Soldering Process**

KEMET's KPS Series devices are compatible with IR reflow techniques. Preheating of these components is recommended to avoid extreme thermal stress. KEMET's recommended profile conditions for IR reflow reflect the profile conditions of the IPC/J-STD-020D standard for moisture sensitivity testing.

To prevent degradation of temperature cycling capability, care must be taken to prevent solder from flowing into the inner side of the lead frames (inner side of "J" lead in contact with the circuit board).

After soldering, the capacitors should be air cooled to room temperature before further processing. Forced air cooling is not recommended.

Hand soldering should be performed with care due to the difficulty in process control. If performed, care should be taken to avoid contact of the soldering iron to the capacitor body. The iron should be used to heat the solder pad, applying solder between the pad and the lead, until reflow occurs. Once reflow occurs, the iron should be removed immediately. (Preheating is required when hand soldering to avoid thermal shock.)

| Profile Feature                                                  | SnPb Assembly       | <b>Pb-Free Assembly</b> |  |

|------------------------------------------------------------------|---------------------|-------------------------|--|

| Preheat/Soak                                                     |                     |                         |  |

| Temperature Minimum $(T_{smin})$                                 | 100°C               | 150°C                   |  |

| Temperature Maximum (T <sub>Smax</sub> )                         | 150°C               | 200°C                   |  |

| Time $(t_s)$ from $T_{smin}$ to $T_{smax}$ )                     | 60 - 120 seconds    | 60 - 120 seconds        |  |

| Ramp-up Rate $(T_L \text{ to } T_P)$                             | 3°C/seconds maximum | 3°C/seconds maximum     |  |

| Liquidous Temperature (T <sub>L</sub> )                          | 183°C               | 217°C                   |  |

| Time Above Liquidous (t <sub>L</sub> )                           | 60 – 150 seconds    | 60 - 150 seconds        |  |

| Peak Temperature (T <sub>P</sub> )                               | 235°C               | 250°C                   |  |

| Time within 5°C of Maximum<br>Peak Temperature (t <sub>p</sub> ) | 20 seconds maximum  | 10 seconds maximum      |  |

| Ramp-down Rate $(T_p \text{ to } T_L)$                           | 6°C/seconds maximum | 6°C/seconds maximum     |  |

| Time 25°C to Peak<br>Temperature                                 | 6 minutes maximum   | 8 minutes maximum       |  |

Note: All temperatures refer to the center of the package, measured on the package body surface that is facing up during assembly reflow.

## Table 4 - Performance & Reliability: Test Methods and Conditions

| Stress                 | Reference                 | Test or Inspection Method                                                                                                                                                                                                                              |  |  |  |

|------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Terminal Strength      | JIS-C-6429                | Appendix 1, Note: Force of 1.8 kg for 60 seconds.                                                                                                                                                                                                      |  |  |  |

| Board Flex             | JIS-C-6429                | Appendix 2, Note: 5.0 mm minimum                                                                                                                                                                                                                       |  |  |  |

|                        |                           | Magnification 50 X. Conditions:                                                                                                                                                                                                                        |  |  |  |

| 0-141:1:4              | L OTD OOG                 | a) Method B, 4 hours at 155°C, dry heat at 235°C                                                                                                                                                                                                       |  |  |  |

| Solderability          | J-STD-002                 | b) Method B at 215°C category 3                                                                                                                                                                                                                        |  |  |  |

|                        |                           | c) Method D, category 3 at 250°C                                                                                                                                                                                                                       |  |  |  |

| Temperature Cycling    | JESD22 Method JA-104      | 1,000 cycles (-55°C to +125°C). Measurement at 24 hours +/-4 hours after test conclusion.                                                                                                                                                              |  |  |  |

| Diagod Humaidia.       | MIL-STD-202 Method        | Load Humidity: 1,000 hours 85°C/85% RH and 200 VDC maximum. Add 100 K ohm resistor Measurement at 24 hours +/-4 hours after test conclusion.                                                                                                           |  |  |  |

| Biased Humidity        | 103                       | Low Volt Humidity: 1,000 hours 85°C/85% RH and 1.5 V. Add 100 K ohm resistor. Measurement at 24 hours +/-4 hours after test conclusion.                                                                                                                |  |  |  |

| Moisture Resistance    | MIL-STD-202 Method<br>106 | t = 24 hours/cycle. Steps 7a and 7b not required.<br>Measurement at 24 hours +/-4 hours after test conclusion.                                                                                                                                         |  |  |  |

| Thermal Shock          | MIL-STD-202 Method<br>107 | -55°C/+125°C. Note: Number of cycles required - 300. Maximum transfer time - 20 seconds. Dwell time - 15 minutes. Air-Air.                                                                                                                             |  |  |  |

| High Temperature Life  | MIL-STD-202 Method<br>108 | 1,000 hours at 125°C with rated voltage applied.                                                                                                                                                                                                       |  |  |  |

| Storage Life           | MIL-STD-202 Method<br>108 | 150°C, 0 VDC for 1,000 hours.                                                                                                                                                                                                                          |  |  |  |

| Vibration              | MIL-STD-202 Method<br>204 | 5 g's for 20 minutes, 12 cycles each of 3 orientations. Note: Use 8" X 5" PCB 0.031" thick, 7 secure points on one long side and 2 secure points at corners of opposite sides. Parts mounted within 2" from any secure point. Test from 10 – 2,000 Hz. |  |  |  |

| Mechanical Shock       | MIL-STD-202 Method<br>213 | Figure 1 of Method 213, Condition F.                                                                                                                                                                                                                   |  |  |  |

| Resistance to Solvents | MIL-STD-202 Method<br>215 | Add aqueous wash chemical, OKEM Clean or equivalent.                                                                                                                                                                                                   |  |  |  |

# **Storage and Handling**

Ceramic chip capacitors should be stored in normal working environments. While the chips themselves are quite robust in other environments, solderability will be degraded by exposure to high temperatures, high humidity, corrosive atmospheres, and long term storage. In addition, packaging materials will be degraded by high temperature—reels may soften or warp and tape peel force may increase. KEMET recommends that maximum storage temperature not exceed 40°C and maximum storage humidity not exceed 70% relative humidity. Temperature fluctuations should be minimized to avoid condensation on the parts and atmospheres should be free of chlorine and sulfur bearing compounds. For optimized solderability chip stock should be used promptly, preferably within 1.5 years of receipt.

#### Construction

# **Product Marking**

Laser marking option is not available on:

- COG, Ultra Stable X8R and Y5V dielectric devices

- EIA 0402 case size devices

- EIA 0603 case size devices with Flexible Termination option.

- · KPS Commercial and Automotive grade stacked devices.

These capacitors are supplied unmarked only.

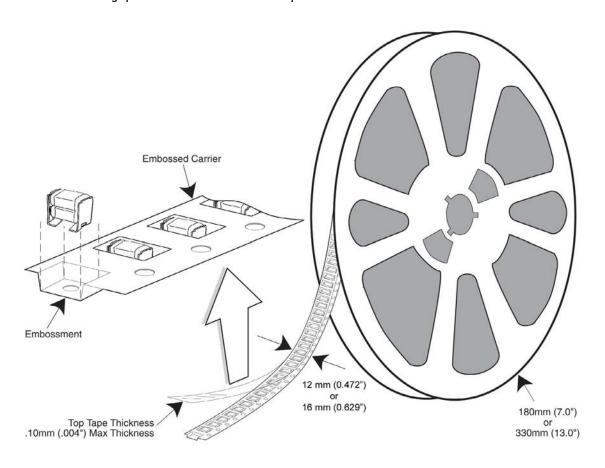

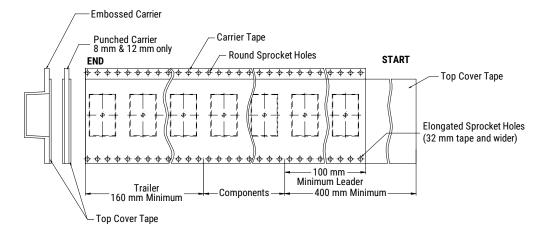

## **Tape & Reel Packaging Information**

KEMET offers multilayer ceramic chip capacitors packaged in 8, 12 and 16 mm tape on 7" and 13" reels in accordance with EIA Standard 481. This packaging system is compatible with all tape-fed automatic pick and place systems. See Table 2 for details on reeling quantities for commercial chips.

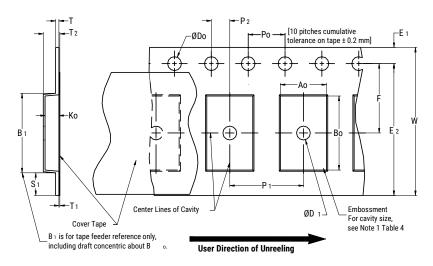

**Table 5 – Carrier Tape Configuration – Embossed Plastic (mm)**

| EIA Case Size     | Tape Size (W)* | Pitch (P <sub>1</sub> )* |  |

|-------------------|----------------|--------------------------|--|

| 01005 - 0402      | 8              | 2                        |  |

| 0603 - 1210       | 8              | 4                        |  |

| 1805 - 1808       | 12             | 4                        |  |

| ≥ 1812            | 12             | 8                        |  |

| KPS 1210          | 12             | 8                        |  |

| KPS 1812 & 2220   | 16             | 12                       |  |

| Array 0508 & 0612 | 8              | 4                        |  |

<sup>\*</sup>Refer to Figure 1 for W and  $P_1$  carrier tape reference locations.

<sup>\*</sup>Refer to Table 5 for tolerance specifications.

## Figure 1 - Embossed (Plastic) Carrier Tape Dimensions

# **Table 6 – Embossed (Plastic) Carrier Tape Dimensions**

Metric will govern

|           | Constant Dimensions — Millimeters (Inches) |                                  |                            |                           |                            |                       |                                  |                                                  |                           |  |  |

|-----------|--------------------------------------------|----------------------------------|----------------------------|---------------------------|----------------------------|-----------------------|----------------------------------|--------------------------------------------------|---------------------------|--|--|

| Tape Size | D <sub>0</sub>                             | D <sub>1</sub> Minimum<br>Note 1 | E <sub>1</sub>             | P <sub>0</sub>            | P <sub>2</sub>             | R Reference<br>Note 2 | S <sub>1</sub> Minimum<br>Note 3 | T<br>Maximum                                     | T <sub>1</sub><br>Maximim |  |  |

| 8 mm      |                                            | 1.0<br>(0.039)                   |                            |                           |                            | 25.0<br>(0.984)       |                                  |                                                  |                           |  |  |

| 12 mm     | 1.5+0.10/0.0-0.0<br>(0.059+0.004/-0.0)     | 1.5                              | 1.75±0.10<br>(0.069±0.004) | 4.0±0.10<br>(0.157±0.004) | 2.0±0.05<br>(0.079±0.002)  | 30                    | 0.600<br>(0.024)                 | 0.600<br>(0.024)                                 | 0.100<br>(0.004)          |  |  |

| 16 mm     |                                            | (0.059)                          |                            |                           |                            | (1.181)               |                                  |                                                  |                           |  |  |

|           | Variable Dimensions — Millimeters (Inches) |                                  |                            |                           |                            |                       |                                  |                                                  |                           |  |  |

| Tape Size | Pitch                                      | B <sub>1</sub> Maximum<br>Note 4 | E <sub>2</sub> Minimum     | F                         | P <sub>1</sub>             | $T_{2}$ Maximum       | W<br>Maximum                     | A <sub>0</sub> , B <sub>0</sub> & K <sub>0</sub> |                           |  |  |

| 8 mm      | Single (4 mm)                              | 4.35<br>(0.171)                  | 6.25<br>(0.246)            | 3.5±0.05<br>(0.138±0.002) | 4.0±0.10<br>(0.157±0.004)  | 2.5<br>(0.098)        | 8.3<br>(0.327)                   |                                                  |                           |  |  |

| 12 mm     | Single (4 mm) &<br>Double (8 mm)           | 8.2<br>(0.323)                   | 10.25<br>(0.404)           | 5.5±0.05<br>(0.217±0.002) | 8.0±0.10<br>(0.315±0.004)  | 4.6<br>(0.181)        | 12.3<br>(0.484)                  | Not                                              | e 5                       |  |  |

| 16 mm     | Triple (12 mm)                             | 12.1<br>(0.476)                  | 14.25<br>(0.561)           | 7.5±0.05<br>(0.138±0.002) | 12.0±0.10<br>(0.157±0.004) | 4.6<br>(0.181)        | 16.3<br>(0.642)                  |                                                  |                           |  |  |

- 1. The embossment hole location shall be measured from the sprocket hole controlling the location of the embossment. Dimensions of embossment location and hole location shall be applied independent of each other.

- 2. The tape with or without components shall pass around R without damage (see Figure 5).

- 3. If  $S_1 < 1.0$  mm, there may not be enough area for cover tape to be properly applied (see EIA Standard 481 paragraph 4.3 section b).

- 4.  $B_1$  dimension is a reference dimension for tape feeder clearance only.

- 5. The cavity defined by  $A_{o}$ ,  $B_{o}$  and  $K_{o}$  shall surround the component with sufficient clearance that:

- (a) the component does not protrude above the top surface of the carrier tape.

- (b) the component can be removed from the cavity in a vertical direction without mechanical restriction, after the top cover tape has been removed.

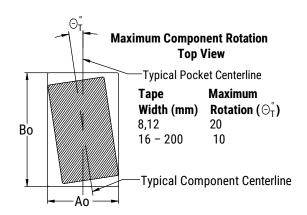

- (c) rotation of the component is limited to 20° maximum for 8 and 12 mm tapes and 10° maximum for 16 mm tapes (see Figure 2).

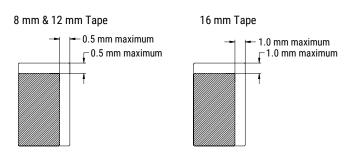

- (d) lateral movement of the component is restricted to 0.5 mm maximum for 8 and 12 mm wide tape and to 1.0 mm maximum for 16 mm tape (see Figure 3).

- (e) for KPS Series product,  $A_n$  and  $B_n$  are measured on a plane 0.3 mm above the bottom of the pocket.

- (f) see Addendum in EIA Standard 481 for standards relating to more precise taping requirements.

# **Packaging Information Performance Notes**

1. Cover Tape Break Force: 1.0 Kg minimum.

2. Cover Tape Peel Strength: The total peel strength of the cover tape from the carrier tape shall be:

| Tape Width   | Peel Strength                    |  |

|--------------|----------------------------------|--|

| 8 mm         | 0.1 to 1.0 Newton (10 to 100 gf) |  |

| 12 and 16 mm | 0.1 to 1.3 Newton (10 to 130 gf) |  |

The direction of the pull shall be opposite the direction of the carrier tape travel. The pull angle of the carrier tape shall be 165° to 180° from the plane of the carrier tape. During peeling, the carrier and/or cover tape shall be pulled at a velocity of 300 ±10 mm/minute.

3. Labeling: Bar code labeling (standard or custom) shall be on the side of the reel opposite the sprocket holes. Refer to EIA Standards 556 and 624.

## Figure 2 - Maximum Component Rotation

#### **Maximum Component Rotation Side View** Maximum Tape Width (mm) Rotation $(\bigcirc_{s}^{\circ})$ 20 8,12 16 - 5610 72 - 2005

# Figure 3 - Maximum Lateral Movement

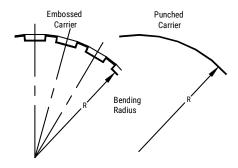

# Figure 4 - Bending Radius

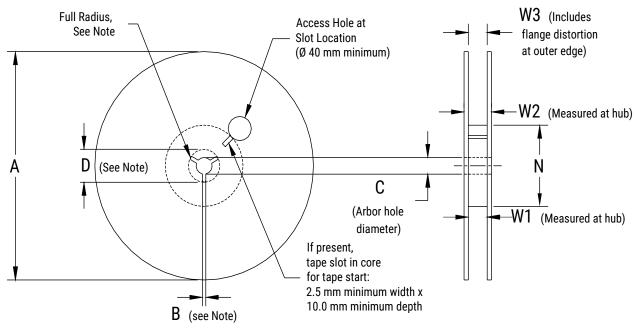

**Figure 5 - Reel Dimensions**

Note: Drive spokes optional; if used, dimensions B and D shall apply.

**Table 7 - Reel Dimensions**

Metric will govern

| Constant Dimensions — Millimeters (Inches) |                                                                   |                                       |                                        |                                                   |  |

|--------------------------------------------|-------------------------------------------------------------------|---------------------------------------|----------------------------------------|---------------------------------------------------|--|

| Tape Size                                  | A                                                                 | B Minimum                             | С                                      | D Minimum                                         |  |

| 8 mm                                       | 178 ±0.20<br>(7.008 ±0.008)<br>or<br>330 ±0.20<br>(13.000 ±0.008) | 1.5<br>(0.059)                        | 13.0 +0.5/-0.2<br>(0.521 +0.02/-0.008) | 20.2<br>(0.795)                                   |  |

| 12 mm                                      |                                                                   |                                       |                                        |                                                   |  |

| 16 mm                                      |                                                                   |                                       |                                        |                                                   |  |

| Variable Dimensions — Millimeters (Inches) |                                                                   |                                       |                                        |                                                   |  |

| Tape Size                                  | N Minimum                                                         | W <sub>1</sub>                        | W <sub>2</sub> Maximum                 | W <sub>3</sub>                                    |  |

| 8 mm                                       | 50<br>(1.969)                                                     | 8.4 +1.5/-0.0<br>(0.331 +0.059/-0.0)  | 14.4<br>(0.567)                        | Shall accommodate tape width without interference |  |

| 12 mm                                      |                                                                   | 12.4 +2.0/-0.0<br>(0.488 +0.078/-0.0) | 18.4<br>(0.724)                        |                                                   |  |

| 16 mm                                      |                                                                   | 16.4 +2.0/-0.0<br>(0.646 +0.078/-0.0) | 22.4<br>(0.882)                        |                                                   |  |

## Figure 6 - Tape Leader & Trailer Dimensions

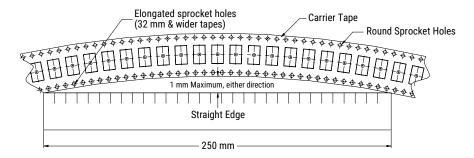

# Figure 7 - Maximum Camber

## **KEMET Electronic Corporation Sales Offices**

For a complete list of our global sales offices, please visit www.kemet.com/sales.

#### **Disclaimer**

All product specifications, statements, information and data (collectively, the "Information") in this datasheet are subject to change. The customer is responsible for checking and verifying the extent to which the Information contained in this publication is applicable to an order at the time the order is placed.

All Information given herein is believed to be accurate and reliable, but it is presented without guarantee, warranty, or responsibility of any kind, expressed or implied.

Statements of suitability for certain applications are based on KEMET Electronics Corporation's ("KEMET") knowledge of typical operating conditions for such applications, but are not intended to constitute – and KEMET specifically disclaims – any warranty concerning suitability for a specific customer application or use. The Information is intended for use only by customers who have the requisite experience and capability to determine the correct products for their application. Any technical advice inferred from this Information or otherwise provided by KEMET with reference to the use of KEMET's products is given gratis, and KEMET assumes no obligation or liability for the advice given or results obtained.

Although KEMET designs and manufactures its products to the most stringent quality and safety standards, given the current state of the art, isolated component failures may still occur. Accordingly, customer applications which require a high degree of reliability or safety should employ suitable designs or other safeguards (such as installation of protective circuitry or redundancies) in order to ensure that the failure of an electrical component does not result in a risk of personal injury or property damage.

Although all product-related warnings, cautions and notes must be observed, the customer should not assume that all safety measures are indicted or that other measures may not be required.