# **High-Speed Differential Line Drivers**

#### **Features**

- Sixteen line drivers meet or exceed the requirements of the ANSI EIA/TIA-644 Standard

- Designed for signaling rates up to 500 Mbps with very low radiation (EMI)

- Low voltage differential signaling with typical output voltage of 350mV into:

- $-100\Omega$  load (PI90LV387)

- $-50\Omega$  load (PI90LVB387)

- Propagation delay times less than 2.6ns

- Output skew is less than 150ps

- Part-to-part skew is less than 1.5ns

- 35mW total power dissipation in each driver operating at 200 MHz

- Bus-pin ESD protection exceeds 10kV

- Low voltage TTL (LVTTL) logic inputs are 5V tolerant

- Packaging (Pb-free & Green available):

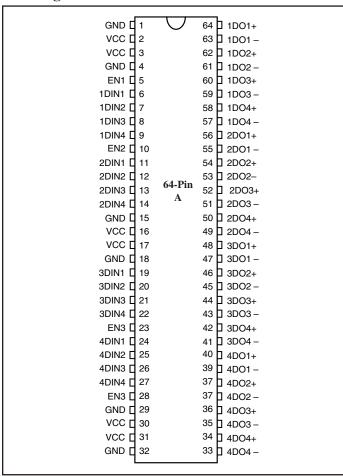

-64-Pin TSSOP (A)

## Pin Diagram

### **Description**

PI90LV387/ PI90LVB387 consists of sixteen differential line drivers that implement the electrical characteristics of low-voltage differential signaling (LVDS). This signaling technique lowers output voltage levels to reduce power, increase switching speeds, and allow operation with a 3V supply rail.

The intended application of this device and signaling technique is for point-to-point baseband (single termination) and multipoint (double termination) data transmission over a controlled impedance media of approximately  $100\Omega$  and  $50\Omega$  (LVB387). The transmission media may be printed-circuit board traces, backplanes, or cables. The large number of drivers integrated into the same substrate, with the low pulse skew of balanced signaling, allows extremely precise timing alignment of clock and data for synchronous parallel data transfers. When used with its companion 16-channel receivers, the PI90LV386 or PI90LVT386, over 400 million data transfers per second in single-edge clocked systems are possible with very little power.

(Note: The ultimate rate and distance of data transfer is dependent upon attenuation characteristics of the media, the noise coupling to the environment, and other system characteristics.)

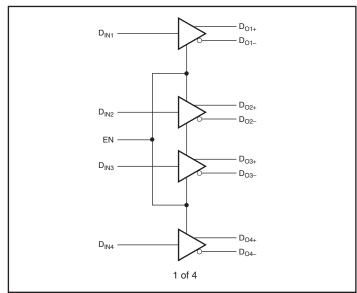

The drivers are enabled in groups of five. When disabled, driver outputs are at a high impedance. Each driver input  $(D_{IN})$  and enable (EN) have an internal pulldown that drives the input to a low level when open circuited.

The parts are characterized for operation from -40°C to 85°C.

# **Block Diagram**

# **Absolute Maximum Ratings**

(Over Operating Free-Air Temperature, unless otherwise noted)<sup>(1)</sup>

| Supply Voltage Range, V <sub>CC</sub> <sup>(2)</sup> | -0.5V to 4V                                                                                                                                           |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage Range: Inputs                                | 0.5V to 6V                                                                                                                                            |

| D <sub>O+</sub> or D <sub>O-</sub>                   | 0.5V to 4V                                                                                                                                            |

| Electrostatic Discharge <sup>(3)</sup> :             |                                                                                                                                                       |

| (D <sub>O+</sub> ,D <sub>O-</sub> and GND)           | Class 3, A: 10kV, B:700V                                                                                                                              |

| (All Pins)                                           | Class 3, A: 8kV, B:600V                                                                                                                               |

| Continuous Power Dissipation                         | (see dissipation rating table)                                                                                                                        |

| Storage Temperature Range                            | 65°C to 150°C                                                                                                                                         |

| Lead Temperature 1.6mm (1/16                         | inch)                                                                                                                                                 |

| from case for 10 seconds                             | 260°C                                                                                                                                                 |

|                                                      | (D <sub>O+</sub> ,D <sub>O-</sub> and GND)<br>(All Pins)<br>Continuous Power Dissipation<br>Storage Temperature Range<br>Lead Temperature 1.6mm (1/16 |

#### **Notes:**

- Stresses beyond those listed under "Absolute Maximum Ratings"

may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other

conditions beyond those indicated under "Recommended Operating

Conditions" is not implied. Exposure to Absolute-Maximum-Rated

conditions for extended periods may affect device reliability.

- All voltage values, except differential I/O bus voltages, are with respect to ground terminal.

- 3. Tested in accordance with MIL-STD-883C Method 3015.7

# **Recommended Operating Conditions**

|                                                | Min. | Nom. | Max. | Units |

|------------------------------------------------|------|------|------|-------|

| Supply Voltage, V <sub>CC</sub>                | 3.0  | 3.3  | 3.6  |       |

| High-level Input Voltage, VIH                  | 2.0  |      |      | V     |

| Low-level Input Voltage, V <sub>IL</sub>       |      |      | 0.8  |       |

| Operating free-air temperature, T <sub>A</sub> | -40  |      | 85   | °C    |

### **Driver Function Table**

| Differential Input | Enables | Outputs           |                    |

|--------------------|---------|-------------------|--------------------|

| $\mathbf{D_{IN}}$  | EN      | D <sub>OUT+</sub> | D <sub>OUT</sub> . |

| Н                  | Н Н     |                   | L                  |

| L                  | Н       | L                 | Н                  |

| X                  | L       | Z                 | Z                  |

| Open               | Н       | L                 | Н                  |

#### **Notes:**

1. H = high level,

L = low level,

X = irrelevent,

Z = high impedance (off)

# Electrical Characteristics Over Recommended Operating Conditions (unless otherwise noted)

| Symbol                          | Parameter                                                              | Test Conditions                                                                                                                                  |     | Min.  | Тур. | Max.  | Units |

|---------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|-------|-------|

| V <sub>OH</sub>                 | Differential output voltage magnitude                                  | $R_{L} = 50\Omega \text{ (LVB)}$ $R_{L} = 100\Omega \text{ (LV)}$ See Figure 1 and 2                                                             |     | 247   | 340  | 454   |       |

| Δ  V <sub>OH</sub>              | Change in differential output voltage magnitude between logic states   |                                                                                                                                                  |     | -50   |      | 50    | mV    |

| Steady-state common-mode output |                                                                        | See Figure 3                                                                                                                                     | LV  | 1.125 |      | 1.375 | V     |

| V <sub>OC(SS)</sub>             | voltage                                                                |                                                                                                                                                  | LVB | 1.000 |      | 1.375 | _     |

| $\Delta V_{OC(SS)}$             | Change in Steady-state common-mode output voltage between logic states | See Figure 3                                                                                                                                     |     | -50   |      | 50    | mV    |

| V <sub>OC(PP)</sub>             | Peak-to-peak common-mode output voltage                                |                                                                                                                                                  |     |       | 50   | 150   | 111 V |

|                                 | Supply Current                                                         | $\begin{aligned} R_L &= 50\Omega \text{ (LVB)} \\ R_L &= 100\Omega \text{ (LV)} \\ \text{Enabled, V}_{IN} &= \text{GND or V}_{CC} \end{aligned}$ | LV  |       | 60   | 78    |       |

| $I_{CC}$                        |                                                                        |                                                                                                                                                  | LVB |       | 122  | 190   | mA    |

| $I_{\mathrm{IH}}$               | High-Level input current                                               | $V_{IH} = 2V$                                                                                                                                    |     |       | 3    | 20    |       |

| $I_{\mathrm{IL}}$               | Low-level input current                                                | $V_{IL} = 0.8V$                                                                                                                                  |     |       | 2    | 10    | μA    |

|                                 | Short-circuit output current                                           | $V_{ODOUT+}$ or $V_{ODOUT-} = 0V$                                                                                                                | LV  |       |      | ±24   |       |

| I.a.a                           |                                                                        |                                                                                                                                                  | LVB |       |      | ±48   | mA    |

| I <sub>OS</sub>                 |                                                                        | $V_{OD} = 0V$                                                                                                                                    | LV  |       |      | ±12   |       |

|                                 |                                                                        |                                                                                                                                                  | LVB |       |      | ±24   |       |

| I <sub>OZ</sub>                 | High-impedance output current                                          | $V_{\rm O} = 0$ V or $V_{\rm CC}$                                                                                                                |     |       |      | ±1    | ۸     |

| I <sub>O(OFF)</sub>             | Power-off output current                                               | $V_{CC} = 0V, V_{O} = 2.4V$                                                                                                                      |     |       |      | ±1    | μA    |

| $C_{IN}$                        | Input capacitance                                                      | $V_I = 0.4 \sin(4E6\pi t) + 0.5V$                                                                                                                |     |       | 6    |       |       |

| Co                              | Output capacitance                                                     | $V_I = 0.4 \sin (4E6\pi t) + 0.5V$ ,<br>Disabled                                                                                                 |     |       | 9.4  |       | pF    |

### Note:

1. All typical values are at 25°C and with a 3.3V supply.

## Switching Characteristics (Over Recommended Operating Conditions, unless otherwise noted)

| Symbol              | Parameter                                                                    | <b>Test Conditions</b>                                                          | Min. | Тур. | Max. | Units |

|---------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>PHL</sub>    | Propagation delay time low-to-high level outputs                             | 0                                                                               |      | 1.8  | 2.6  |       |

| t <sub>PHL</sub>    | Propagation delay time, high-to-low-level outputs                            |                                                                                 | 0.9  | 1.8  | 2.6  | ns    |

| $t_{r}$             | Differential outpu sign rise time                                            | $R_L = 50\Omega \text{ (LVB)}$                                                  | 0.4  | 0.8  | 1.3  |       |

| $t_{\mathrm{f}}$    | Differential output signal fall time                                         | output signal fall time $R_L = 100\Omega \text{ (LV)}$ $C_L = 10 \text{pF}$ 0.4 |      | 0.8  | 1.3  |       |

| t <sub>sk(p)</sub>  | Pulse skew (   tphl - tphl   )                                               | See Figure 4                                                                    |      | 150  | 500  |       |

| t <sub>sk(o)</sub>  | Output skew <sup>(2)</sup>                                                   |                                                                                 |      | 80   | 150  | ps    |

| t <sub>sk(pp)</sub> | Part-to-part skew (3)                                                        |                                                                                 |      |      | 1.5  |       |

| t <sub>PZH</sub>    | Propagation delay time, high impdeance-to high-level output                  |                                                                                 |      | 4.5  | 6.7  |       |

| t <sub>PZL</sub>    | Propagation delay time, high impdeance-to low-level output 3                 |                                                                                 | 3.5  | 5.1  |      |       |

| t <sub>PHZ</sub>    | Propagation delay time, high-level-to-high-impdeance output See Figure 5 3.1 |                                                                                 | 3.1  | 4.6  | ns   |       |

| t <sub>PLZ</sub>    | Propagation delay time, low-level-to-high-impdeance output                   |                                                                                 |      | 3.1  | 4.6  |       |

| $f_{MAX}$           | Maximum operating frequency                                                  |                                                                                 |      | 250  |      | MHz   |

#### **Notes:**

- 1. All typical values are at 25°C and with a 3.3V supply

- 2. t<sub>sk(o)</sub> is the magnitude of the time difference between the t<sub>PLH</sub> or t<sub>PHL</sub> of all drivers of a single device with all of their inputs connected together.

- 3.  $t_{sk(pp)}$  is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits

### **Parameter Measurement Information**

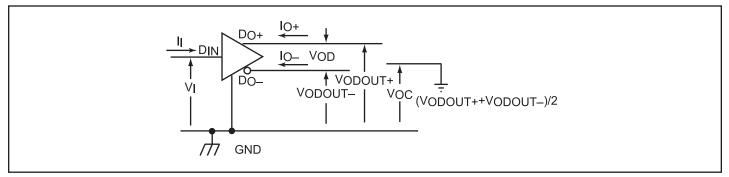

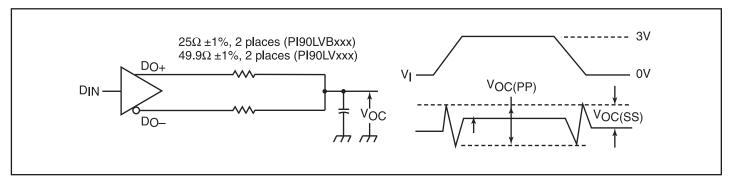

Figure 1. Voltage and Current Definitions

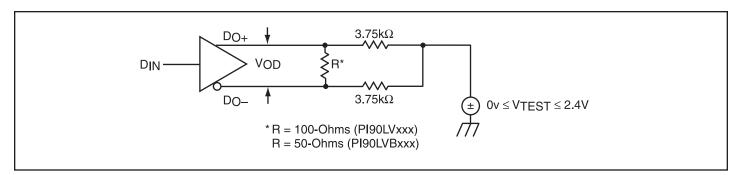

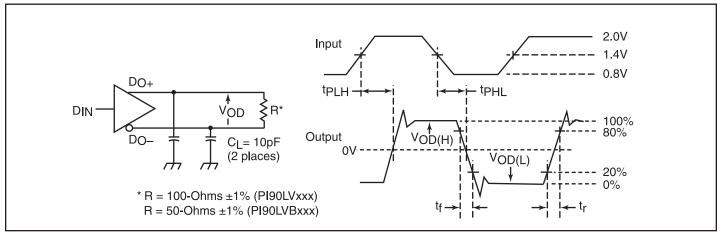

Figure 2. VOD Test Circuit

Figure 3. Test Circuit & Definitions for the Driver Common-Mode Output Voltage

### Note:

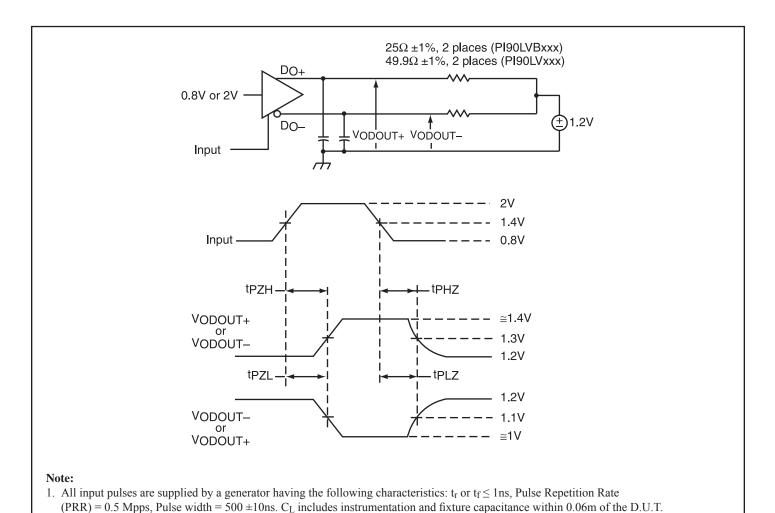

All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$ ns, Pulse Repetition Rate (PRR) = 50 Mpps, Pulse width =  $10 \pm 0.2$ ns.  $C_L$  includes instrumentation and fixture capacitance within 0.06m of the D.U.T. The measurement of VOC(PP) is made on test equipment with a -3dB bandwidth of at least 300MHz.

08-0295 PS8573D 11/11/08

### **Parameter Measurement Information** (continued)

Figure 4. Test Circuit, Timing, & Voltage Definitions for the Differential Output Signal

#### Note:

1. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$ ns, Pulse Repetition Rate (PRR) = 15 Mpps, Pulse width =  $10 \pm 0.2$ ns.  $C_L$  includes instrumentation and fixture capacitance within 0.06m of the D.U.T.

Figure 5. Enable & Disable Time Circuit & Definitions

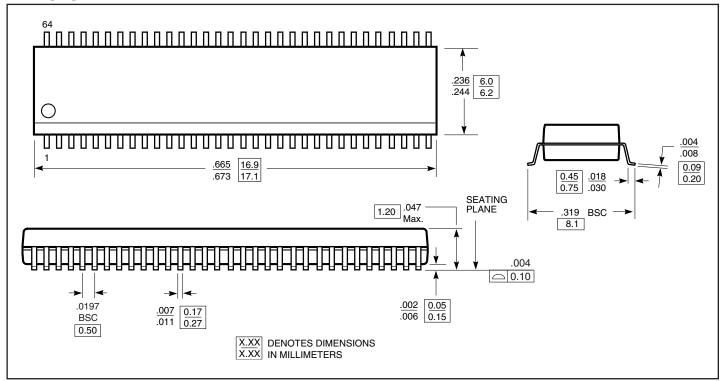

## Packaging Mechanical: 64-Pin TSSOP (A)

# **Ordering Information**

| Ordering Code | Package Code | Package Type                  |

|---------------|--------------|-------------------------------|

| PI90LV387AE   | A            | Pb-free & Green, 64-pin TSSOP |

| PI90LVB387A   | A            | 64-pin TSSOP                  |

| PI90LVB387AE  | A            | Pb-free & Green, 64-pin TSSOP |

#### Notes:

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. Number of Transistors = TBD